还没推出的东西 你测试过了?

直流电 发表于 2010-8-24 18:26

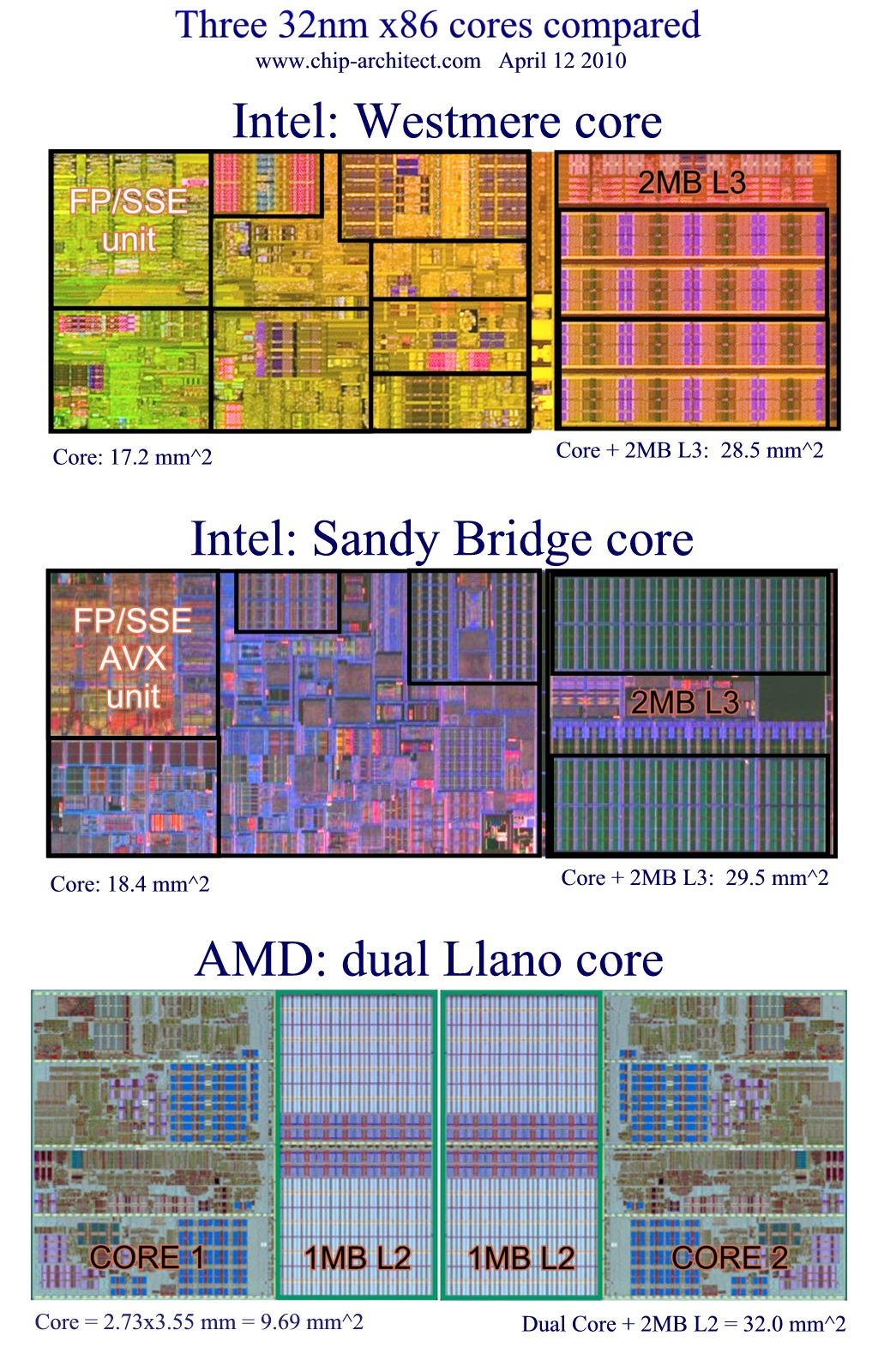

westmere的L2占面积相当小,从照片上看不到整个核心的1/9。也就是说除去L2,westmere将是15平方毫米左右 ...

fpu一直都有自己的load/store单元,---k7开始就是3个浮点单元,两个运算,一个misc(其实就是ld/st)。因为fpu的数据读写与整型部分差别非常大而对延迟很不敏感。注意netburst,所有型号的fpu数据都是只通过L2的,bd也这么做完全顺理成章。

spinup 发表于 2010-8-25 12:25

理论值是加倍。

其实应该比较的是一个128位加乘融合和一个128位乘并一个128位加。

理论上有折扣---加乘单元可能只提供一个端口,换句话说不能同时跑分立的一个加一个乘。

不过也有加成---融合的加乘运算实际比1乘后再1加要快不少。

不过折扣的情况其实挺罕见,但是软件编得好的话加成的情况倒是普遍的。 所以现在普遍使用FMACspinup 发表于 2010-8-25 16:28

我认为你的提法欠妥或相矛盾,乱序是指令级,如果乱序加强,指令并行要加强。线程并行更注重顺序结构,用线程去并行处理“小的顺序事务”收益最大,尤其是将分支事务变成两个甚至多个线程去处理时,这样的收益巨大。

AMD11 发表于 2010-8-25 19:15

fpu一直都有自己的load/store单元,---k7开始就是3个浮点单元,两个运算,一个misc(其实就是ld/st)。因为fpu的数据读写与整型部分差别非常大而对延迟很不敏感。注意netburst,所有型号的fpu数据都是只通过L2的,bd也这么做完全顺理成章。

spinup 发表于 2010-8-25 12:25

认为bd核心的整数性能比k10低,那有2个前提,一是bd的整数单元就是在k10的基础上消去1/3,二是k10的3个alu利用率很高。

而实际上bd的2alu和2agu是独立的,各自拥有完整管线,利用率更高,再结合改进相当大的预取,分支预测、宏融合以及需要重新设计的译码单元,bd核心的整数ipc肯定比k10要高。amd在总结里把单线程性能作为显著提升的要点之一提出来,应当是ipc提高与更先进的turbo模式共同作用的结果。

hammerking 发表于 2010-8-25 19:42

x86的指令发射宽度还是变大了的 3->4。在跑单线程任务时时怎么看也算是大水管进。

AMD应该是把宝押在以后应用程序大都是多线程并行化,大方向还是没错的。目前处理器单线程性能的提高到了怠涨期,即便对intel来说也是如此。

ifu 发表于 2010-8-25 19:50

做单线程时,四发射肯定是为一个core服务,同样2*128fmac也可以被一个core占用。

以你的这个思路,你还是以bd的一个core对比sb的一个core,但假若4模块8核心bd真的能匹敌8核心sb,那intel要哭死了。

hammerking 发表于 2010-8-25 20:04

回复 AMD11

莫非上帝拉出了楼主,让你有了非人的预测能力,靠文字图片就是预测?

你娃有水平就去做CPU啦,光说不做是棒槌,只会臆测就不允许其他说咯嘛?

tanlwowo 发表于 2010-8-25 21:10

如果这个图不是AMD忽悠的话,按核心而论,L1缩水,AGU、ALU缩水,本人**一次,单线程基本没什么提高,甚至不如K10.5,浮点彻底废掉。看来以前的预测还是有效地,AMD想将浮点放在异构上。

另外,按照Bulldozer的架构方式,可能会衍生出一个顺序架构的东西。

以上仅是个人理解,有错误实属难免,不过个人很有信心,等待实物实测证实。, ...

AMD11 发表于 2010-8-24 17:52

如果用小“core”的观点看,发射宽度极度缩小,执行资源虽然也缩水了,可整数资源还是过剩,但是L1的缩小就变得不可理喻,一下子变到了 16KBD/core,相比K10.5的64KBD/core而言差了4倍。难道AMD自信自己的L2上能与Intel比吗?Intel的L2可达到 6~7周期,而且是独享的,并且L1D可是32KB。

根据这个图,可以预测,针对Bulldozer优化程序主要是那些具有良好顺序执行的非浮点密集的程序,这样才能最大地发挥Bulldozer的能力。可惜,服务器上面向事务的程序并不是很符合这个要求,除非优化再优化。但是AMD自身连编译器都做不了,在业界的能力和影响很小。因此,不难推测,Bulldozer的综合能力提高有限,同频下,以模块对K10.5核心,4对4,多线程也就15%~25%的提升,单线程就算了,不说也罢。

AMD11 发表于 2010-8-25 08:29

| 欢迎光临 POPPUR爱换 (https://we.poppur.com/) | Powered by Discuz! X3.4 |