daniel_k 发表于 2012-9-13 19:21

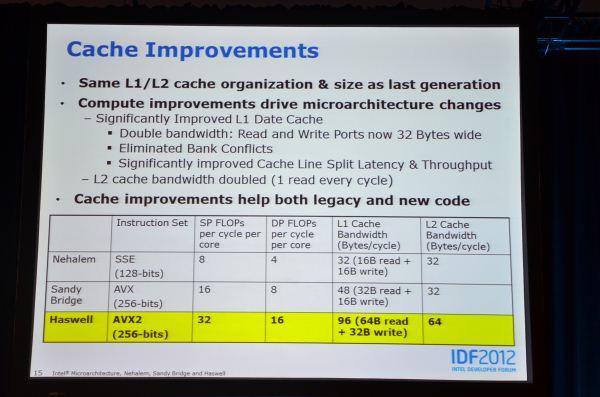

难怪这么彪悍,想想汇编里面到处都是mov jump之类的,一旦内存非相干了效率会提升多少哇[mellow>

即使是 ...

,不要揪我的小辫子),如今看来,还真如此了,Intel真的做了限制,估计在14nm工艺才放开这些限制(推测,错,望斧正)。

,不要揪我的小辫子),如今看来,还真如此了,Intel真的做了限制,估计在14nm工艺才放开这些限制(推测,错,望斧正)。AMD11 发表于 2012-9-15 19:34

http://www.ch_i_p_h_el_l.com/thread-451483-1-1.html

去掉所有的下划线,减号不要去掉。所说的L4也不是 ...

| 欢迎光临 POPPUR爱换 (https://we.poppur.com/) | Powered by Discuz! X3.4 |