acqwer 发表于 2013-10-18 12:12

说以说Z2580 512K*2,瓶颈更明显。

所以爱疯5s烂还是三滴马克烂我们选哪个

所以爱疯5s烂还是三滴马克烂我们选哪个ifu 发表于 2013-10-18 20:58

应该有分析编译结果,例如SFFT(there's something like a 30% reduction in instructions for the A64 co ...

ifu 发表于 2013-10-18 19:48

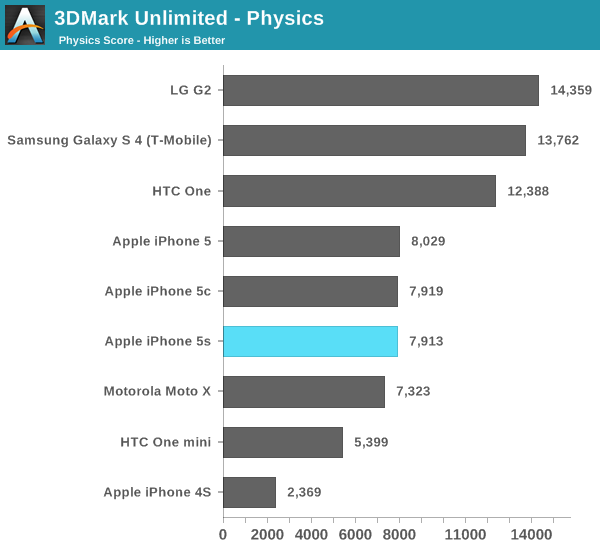

找了一下3dmark官网http://www.3dmark.com/search?locale=zh_CN,没找到查3DMark Unlimited ice storm物理 ...

ifu 发表于 2013-10-18 20:58

应该有分析编译结果,例如SFFT(there's something like a 30% reduction in instructions for the A64 co ...

比同频转战到比同样的L2了么,遮羞布除了洞洞装蕾丝装还有什么花样

比同频转战到比同样的L2了么,遮羞布除了洞洞装蕾丝装还有什么花样

Tempestglen 发表于 2013-10-20 15:14

A7/A6都是1M L2吧。

3dmark的locality工作做得不好,程序写得不好。locality就是程序员的份内工作。这 ...

Tempestglen 发表于 2013-10-20 15:14

A7/A6都是1M L2吧。

3dmark的locality工作做得不好,程序写得不好。locality就是程序员的份内工作。这 ...

the_god_of_pig 发表于 2013-10-20 15:19

咦,3dmark编的不好?3dmark跑在bay trail上怎么没吃鳖啊,是不是intel给钱黑水果啊哈哈哈[biggrin>[bigg ...

Tempestglen 发表于 2013-10-20 16:41

坐等furturemark的试验,用事实打脸!目前futuremark已经证明了A7的新式prefetch被他们完全浪费。只要他们 ...

Now it completely depends on the game as to what kind of load it puts on the CPU, but I would say that "easy" serialized memory access is something most commonly seen in very narrow tasks (file compression, image manipulation) and it doesn't tend to happen in more complex systems like game engines.

能支持t神的”大水果不败神论“了吗?

能支持t神的”大水果不败神论“了吗?Tempestglen 发表于 2013-10-20 18:40

A7当然可以1v2对付那些S800/bt/5420什么的,但是遇到bullet这种随机内存访问的程序, 总不能把1M L2当2M ...

Tempestglen 发表于 2013-10-20 18:50

说了半天, 你是在强调prefetch的重要性,问题是A7的prefetch就是比A6强大得多得多。

prefetch对付loc ...

如果给A7配备2M L2,跑physics也是A15的2倍

Tempestglen 发表于 2013-10-20 18:50

说了半天, 你是在强调prefetch的重要性,问题是A7的prefetch就是比A6强大得多得多。

prefetch对付loc ...

那到底怎样才能跑一万五,要排t神去水果搞cpu layout的还是派ifu去三滴马克做死程?

那到底怎样才能跑一万五,要排t神去水果搞cpu layout的还是派ifu去三滴马克做死程?| 欢迎光临 POPPUR爱换 (https://we.poppur.com/) | Powered by Discuz! X3.4 |