largewc 发表于 2013-10-30 14:44

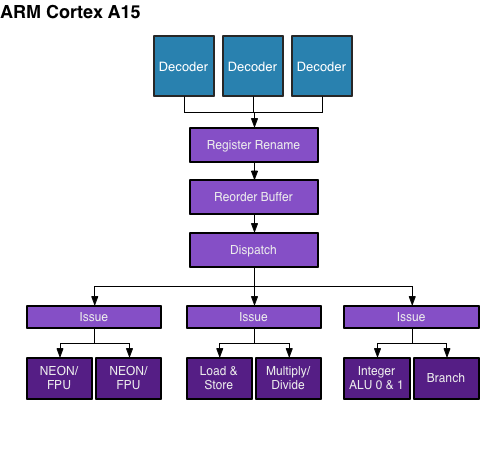

整数比a15多了一组单元,浮点没变,6并发只是提升利用率,可能有少量的提升

这两个都不足与提供翻倍的性 ...

ifu 发表于 2013-10-30 17:01

执行单元是和指令发射端口相匹配的,见原文中four integer adds and two FP adds in parallel

在饱和吞吐 ...

所以堆了一个die size是a15两倍跑三滴马克物理分微增4%的玩意出来么

所以堆了一个die size是a15两倍跑三滴马克物理分微增4%的玩意出来么 这么说a8不上四核跟30m L2估计玩愤怒的小鸟跟百战天虫啥的“物理”游戏要卡出屎了

这么说a8不上四核跟30m L2估计玩愤怒的小鸟跟百战天虫啥的“物理”游戏要卡出屎了 当然L/S还是比A7强的

当然L/S还是比A7强的

532 发表于 2013-10-31 09:33

不是啦,愤怒小鸟那么多物理特效,又没装老黄的显卡能gpu跑物理X,a7的cpu算不过来的啦,L2都卡死了我估计 ...

ifu 发表于 2013-10-31 09:30

haswell也做不到同时发射 4 INT adds+ 2 FP adds当然L/S还是比A7强的

擦才发现这标题还给高亮了,跟隔壁交易区一样黑亮给群众鞭尸围观的么

擦才发现这标题还给高亮了,跟隔壁交易区一样黑亮给群众鞭尸围观的么 小鸟那个说真的,touch4在个别场景一发KO引起太多物体崩塌的话,一样会卡,我也不晓得是不是得i7 5g跑才流畅,台式机上没玩过

小鸟那个说真的,touch4在个别场景一发KO引起太多物体崩塌的话,一样会卡,我也不晓得是不是得i7 5g跑才流畅,台式机上没玩过

最起码也是官方发炎人,前些天还“在此我正式宣布a7 ipc是a6两倍”来着

最起码也是官方发炎人,前些天还“在此我正式宣布a7 ipc是a6两倍”来着four integer adds and two FP adds in parallel

You can also perform up to two loads or stores per clock.

目前看来A7在平板电脑和手机所关注的浏览器性能上相比A6提升了一倍性能,从这个意义上说A7是成功的。

Tempestglen 发表于 2013-10-31 21:01

也就是说3dmark physics这种复杂程度的场景所需要的working set,对于双核A7的1M L2来说太大了?所以随机 ...

Tempestglen 发表于 2013-10-31 21:12

http://ark.intel.com/products/71459/Intel-Core-i7-3630QM-Processor-6M-Cache-up-to-3_40-GHz

3630qm ...

这样才知道哪个数据规模是拐点以及消除了访存屏障后和haswell的差距究竟有多大。

这样才知道哪个数据规模是拐点以及消除了访存屏障后和haswell的差距究竟有多大。Tempestglen 发表于 2013-10-31 21:12

http://ark.intel.com/products/71459/Intel-Core-i7-3630QM-Processor-6M-Cache-up-to-3_40-GHz

3630qm ...

Tempestglen 发表于 2013-10-31 21:31

如果3dmark physics(ice storm)的working set大于2M比如是3M,那么S所有sox都卡在IO瓶颈上, S800/5420 ...

Tempestglen 发表于 2013-10-31 22:53

1)futuremark的人说psolve link消耗了几乎所有的cpu时间。

2)我刚才举了cortex A15和cyclone的例子。 ...

| 欢迎光临 POPPUR爱换 (https://we.poppur.com/) | Powered by Discuz! X3.4 |