原帖由 Edison 于 2006-9-26 10:01 发表

我已经更改为互连结构了。

Note that these cores are almost certainly in-order, and are certainly less complex than the Cell processor's SPEs

原帖由 RacingPHT 于 2006-9-27 10:28 发表

不行的, 顶多可以模拟shader的数学运算. 其实CELL出来以后, GPU数学运算的优势就开始减弱了.

GPU的优势其实是每个TMU 1cycle的4 * 4值采样+三个线性插值. 再加上各向异性过滤这样的东西, 能把CPU弄死的.

原帖由 potomac 于 2006-9-27 22:26 发表

找了半天。原来偶帖子被移进来了。:funk:

不过还是没人回答偶的问题啊。:(

原帖由 Edison 于 2006-9-26 18:46 发表

FPGA模拟IA32,跑2MHz不够,主板不需要怎样讲究。

原帖由 罗菜鸟 于 2006-9-27 22:41 发表

90nm的FPGA的频率能够跑多少?

原帖由 RacingPHT 于 2006-9-28 10:38 发表

我就是觉得TMU应该由硬件电路做的, 而不是通用部件:)

原帖由 Edison 于 2006-9-27 22:34 发表

Intel的TerPro Aject是把TMU也集成进去,和PS2的做法截然不同,倒是和SONY当初构思的CELL应用方案类似。

原帖由 RacingPHT 于 2006-9-28 13:37 发表

如果TMU占5%不到的核心面积, 怎么知道不合算呢.

要芯片面积合算, 为什么用x86呢。帐不是那么容易算的吧.

原帖由 RacingPHT 于 2006-9-28 13:43 发表

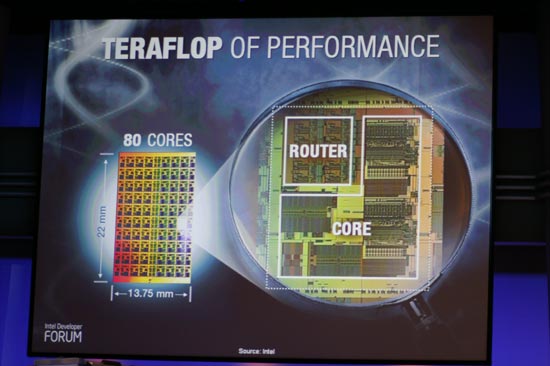

麻烦你看一看那个芯片布局示意图, OK?

3 / 64 = 4.7%

原帖由 RacingPHT 于 2006-9-28 13:53 发表

你完全错了.

集成显卡可以做Linpak吗? 可以算PI吗? 可以让视频编码速度提高数十倍吗? 可以任意做CPU擅长的事情吗? 不行。

这个many core, 可是货真价实的CPU core, 想做什么都可以。本质不同了。

Inte ...

原帖由 RacingPHT 于 2006-9-28 14:33 发表

这招其实我觉得蛮厉害.

至于显卡的shader的通用化, 只要你了解GPU的流水线结构, 就大概会同意, 它和性能相近的core相比完全没有竞争力可言.

与PC上应用面越来越窄的高端GPU相比, 我觉得many core的杀伤力 ...

原帖由 potomac 于 2006-10-2 09:34 发表

这个bus没看懂。有没有这次IDF的完整PDF下载?:unsure:

原帖由 RacingPHT 于 2006-10-3 12:11 发表

单纯图形性能, 这个东西肯定不如专用电路的, 虽然以后flops可能差距不会太大, 但是很多东西, 比如硬件filter, interpolator, MSAA unit, 隐藏延迟的TMU hardware thread, CPU都不好实现。GPU的高端需求, 肯定是 ...

| 欢迎光临 POPPUR爱换 (https://we.poppur.com/) | Powered by Discuz! X3.4 |